### **Toward a m<sup>3</sup> DHCAL prototype** with an integrated readout

### Vincent Boudry LLR, École polytechnique

*ECFA 2008 Warsaw 9-12 june 2008*

## **Overview**

- Case for a digital calorimeter

- Detectors :

- ▶ µMEGAS

- Characterisation

- ► RPC

- Digital Readout by ASICs

- ► HARDROC

- ► DIRAC

- Integration & Debug Card: DHCAL1 & readout

- Cosmic tests

- 1 m<sup>2</sup> prototype

- Validation of large surface detector & readout

- 1 m<sup>3</sup> prototype

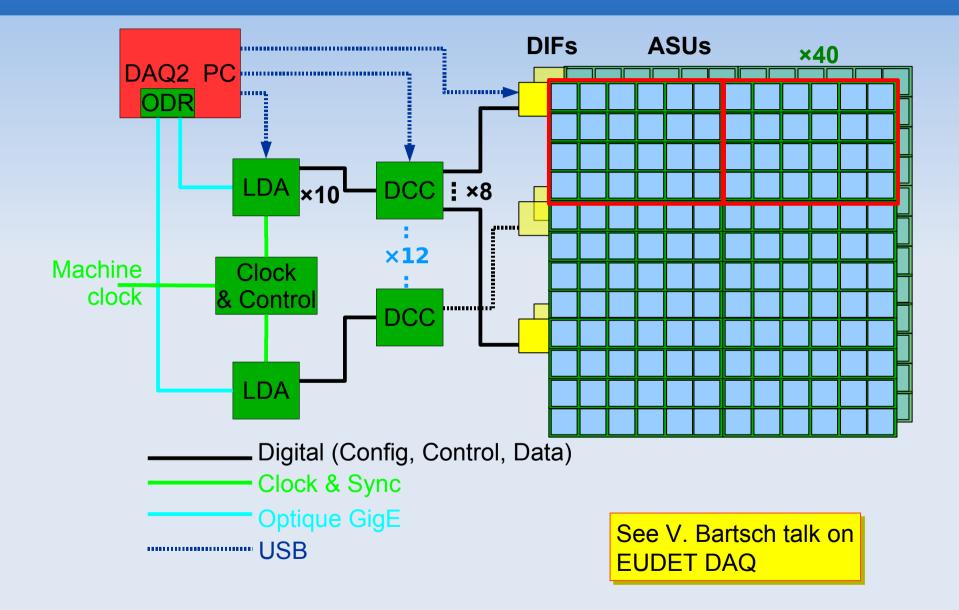

- First use new gen. of EUDET DAQ2

- ► see V. Bartsch talk

- Efforts of integration in ILD & SiD

- Mechanical & simulation

- See corresponding talks

### Case for a Digital HAdronic CALorimeter

### 1 or 2 bits of information per cell

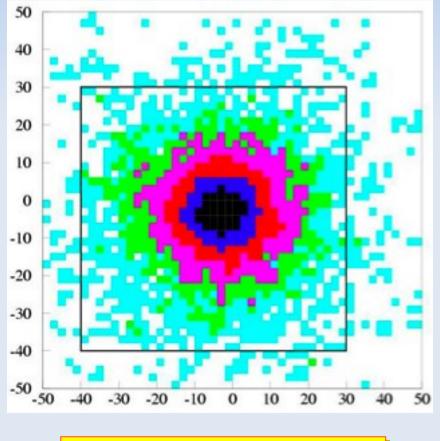

- Finer granularity  $\rightarrow$  1×1 cm<sup>2</sup> × 40 planes

- Ideal for a PFA approach

- Cheaper, simpler, more robust detectors

- ♦ GRPC, µMEGAS, GEM's

- Gaseous detectors

- insensitivity to neutrons

- narrower showers (99% of hits in 70×70 cm<sup>2</sup> for 100 GeV π)

- suppression of big fluctuations

- Recovery of information ?

- counting

- improvement: 3 thresholds

- topology

- clustering

See note LC-DET-2004-029

Vincent.Boudry@in2p3.fr Toward a m<sup>3</sup> DHCAL prototype – ECFA 2008, June 9-12, 2008, Warsaw

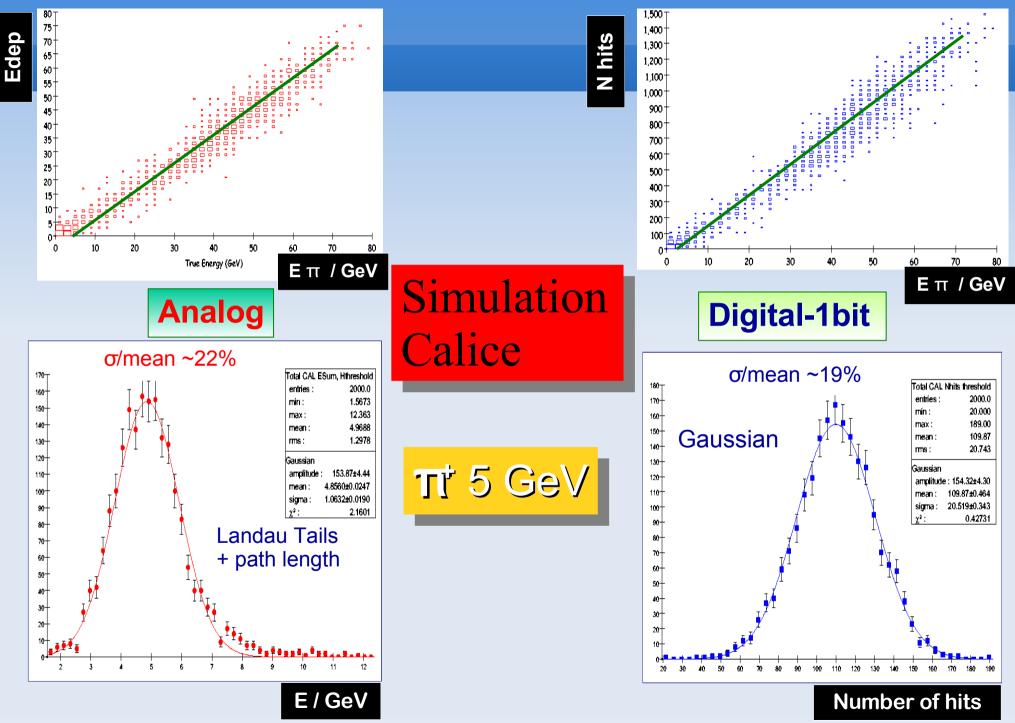

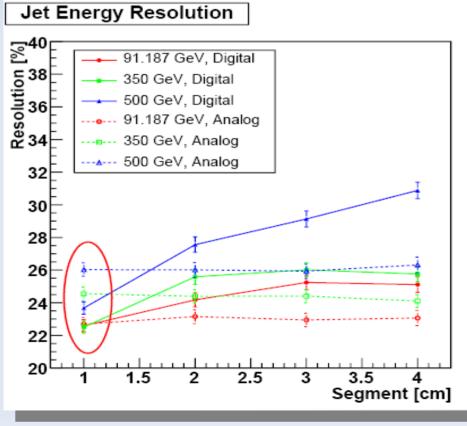

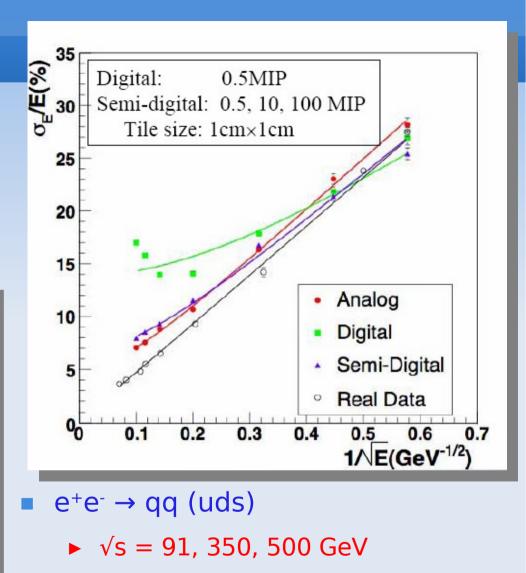

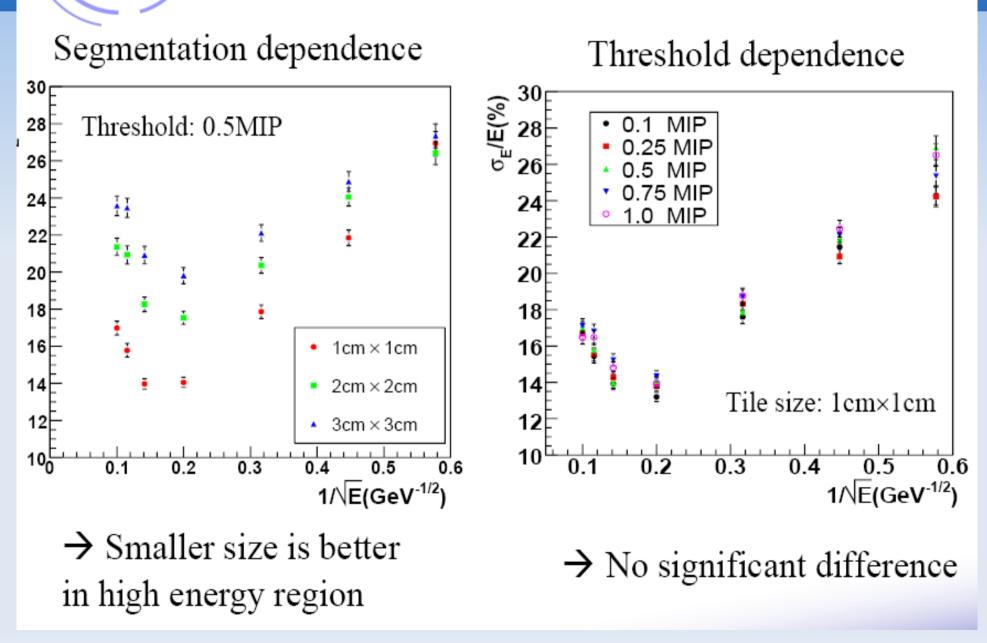

# **Resolution studies**

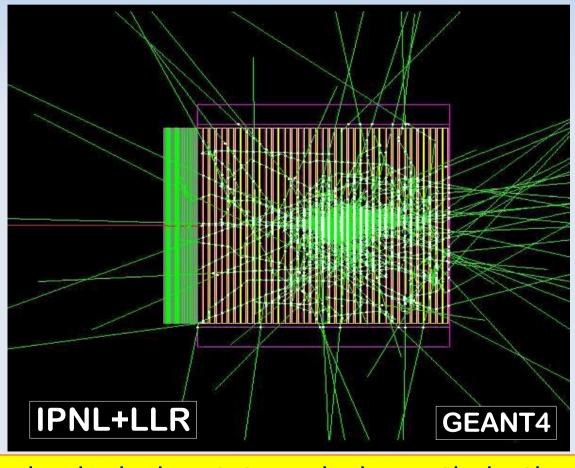

GLD HCAL study by KEK Group

- 3 thresholds (0.5, 10, 100 MIP's)

- 1×1 cm<sup>2</sup> tiles

- 1 bit better @ low E

- Assuming Perfect PFA

- → Better jet resolution

H MATSUNAGA Pramana J. Phys., Vol. 69,

Vincent.Boudry@in2p3.fr Toward a m<sup>3</sup> DHCAL prototype – E No. 6, December 2007

# **DHCAL's in the Calice Collaboration**

USA:

See pres. of J. Repond

- ► GRPC / GEMs

- Physics prototype

- Binary (1 bit) R/O

### EUROPE: \*

- ► GRPC / µMEGAS

- Technological prototype

- embedded RO electronics

- ► Semi digital R/O

France, Russia, Spain

CIEMAT, IHEP, IPNL, LAL, LAPP, LLR

- ~25 persons

- Funding:

CNRS/IN2P3 + EUDET + French ANR

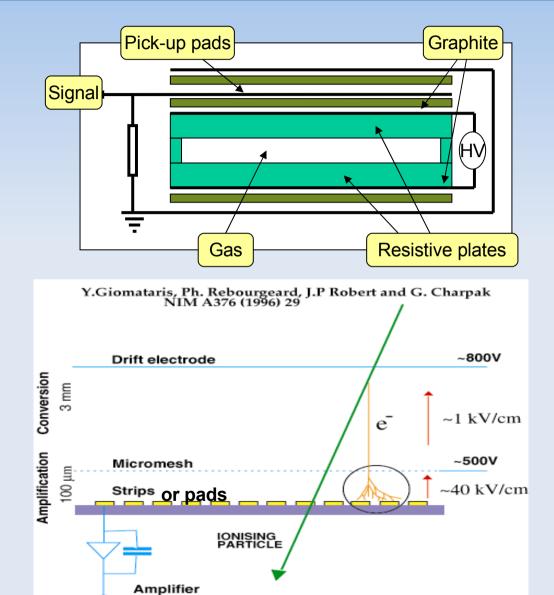

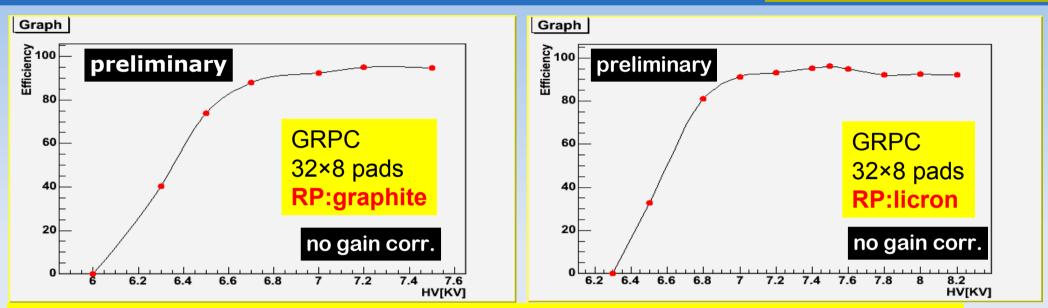

# **Gaseous detector technology**

- Detectors

- ► GRPC (IHEP+IPNL)

- simple, robust, rate ≤ 100 Hz/cm<sup>2</sup>

- μMEGAS: (LAPP)

- robust, high rates, delicate implementation

Vincent.Boudry@in2p3.fr Toward a m<sup>3</sup> DHCAL prototype – ECFA 2008, June 9-12, 2008, Warsaw

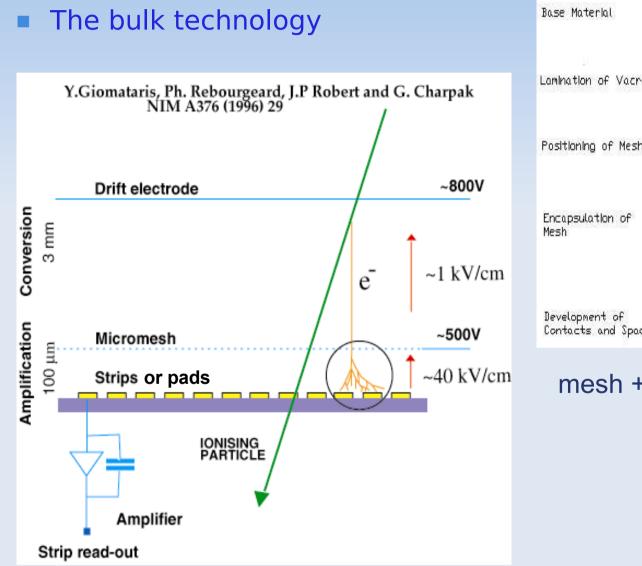

Strip read-out

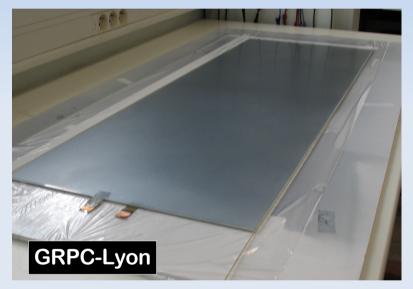

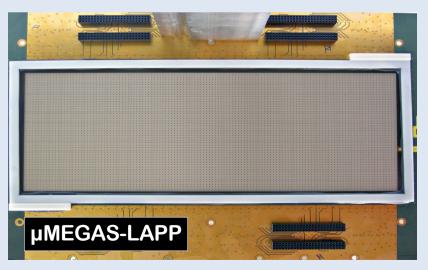

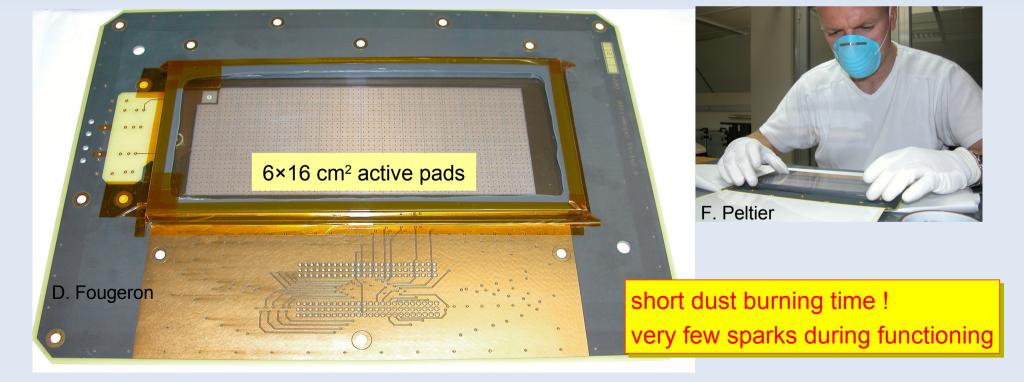

# **Detectors: prototypes**

#### GRPC:

8×8, 32×8, 50×32, 100×32, 100×100

1 cm<sup>2</sup>-pad : already produced and tested.

- μMEGAS:

- 16×6, 32×8, 32×12

1 cm<sup>2</sup>-pads: produced and tested.

- Larger size detectors are under development

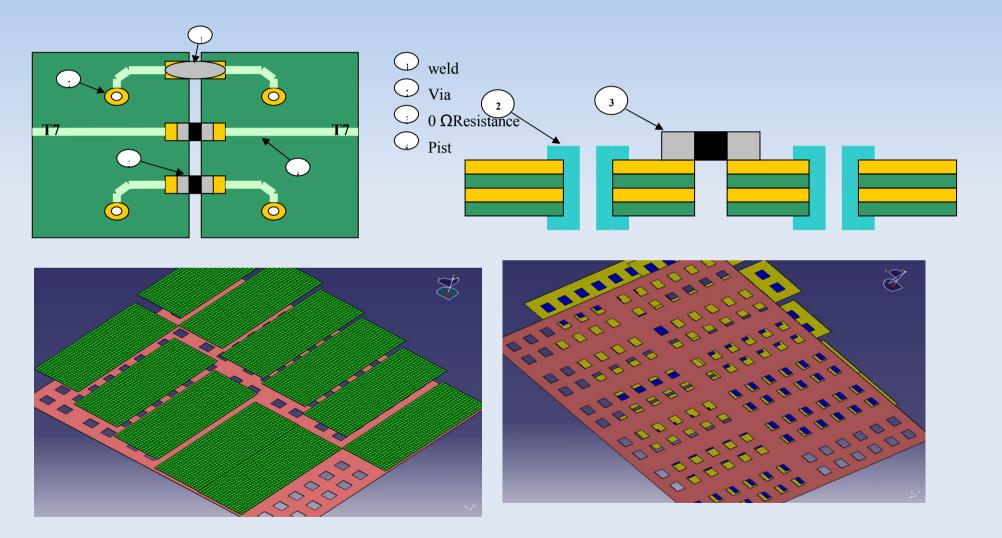

# **µMegas Prototypes**

- PCB rooting with great care (4 layers)

- Stainless Steel top with holes for X-rays

- 5 μm thick copper drift cathode

- Chamber assembly in clean environment

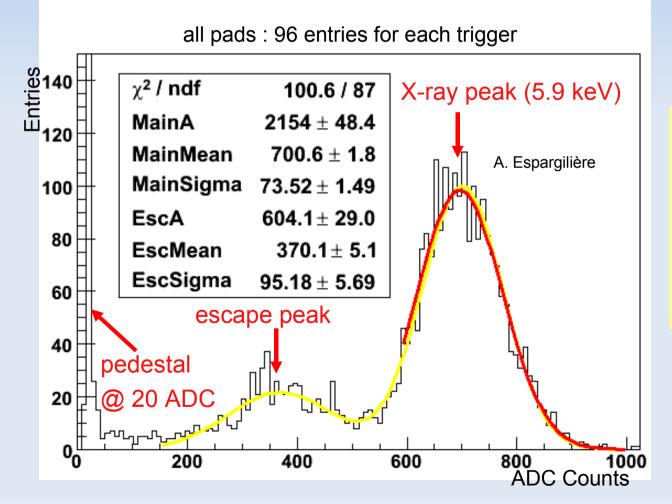

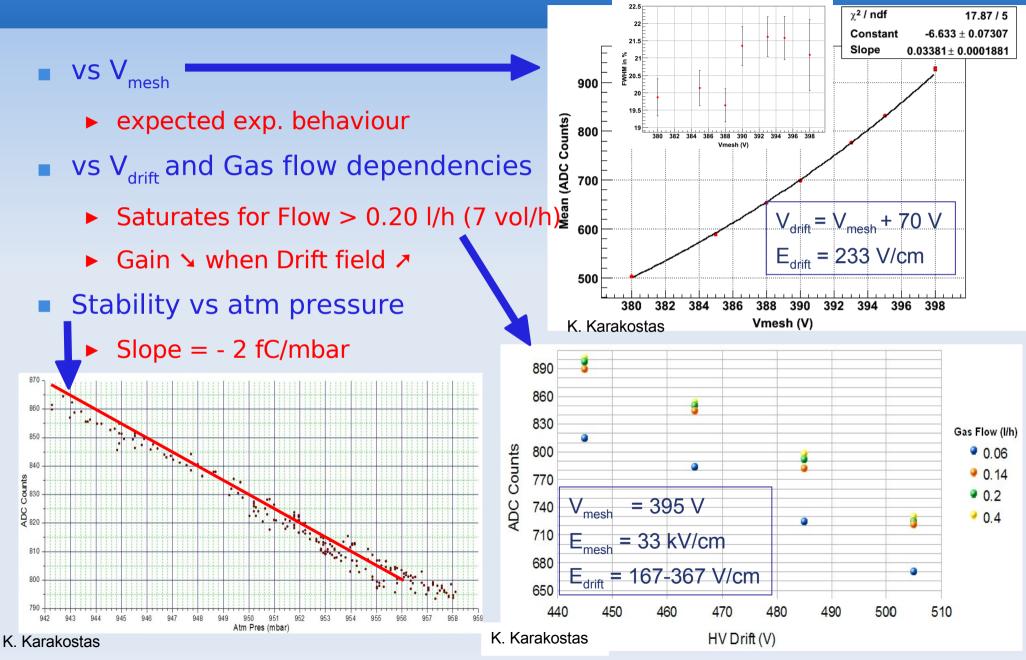

# µMEGAS: X rays response

- <sup>55</sup>Fe source (5.9 keV  $\approx$  228 e- in drift volume)

- Trigger on mesh : preamp (T output) + fast ampli

```

V_{mesh} = 420 VV_{drift} = 470 VE_{mesh} = 35 \text{ kV/cm}E_{drift} = 167 \text{ V/cm}

```

Gassiplex Readout : Peak = 680 ADC cnts = 996 mV ≈277 fC Gain ≈7600 FWHM = 25.5%

T2K(same techno) : FWHM = 26%

# **µMEGAS: X rays response**

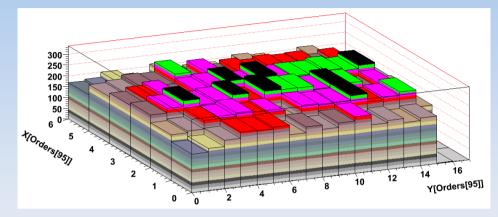

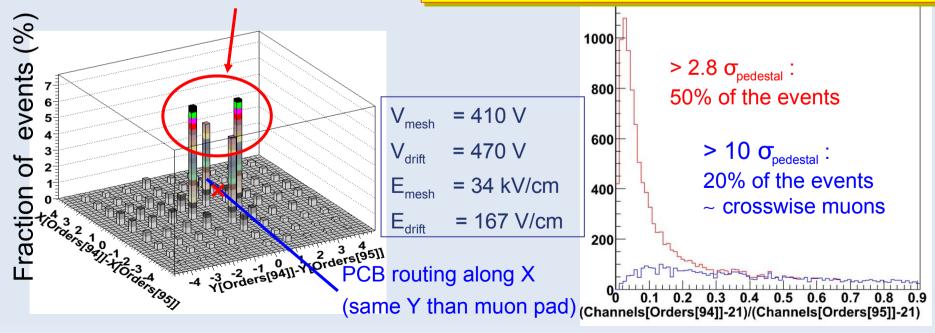

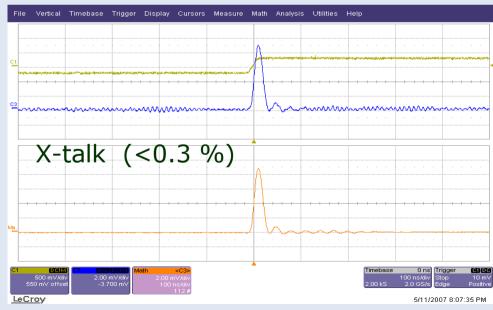

# **µMEGAS: X-talk from Cosmics**

- Trig on 3 scint. coinc.

- MIPs selections:

- Charge ~ 32 fC

Gain ~ 6900

- X-talk:

- 20% of events have events to highest E pad

#### Chamber mapping (geographic occupancy)

#### Signal(second pad) / Signal(muon pad)

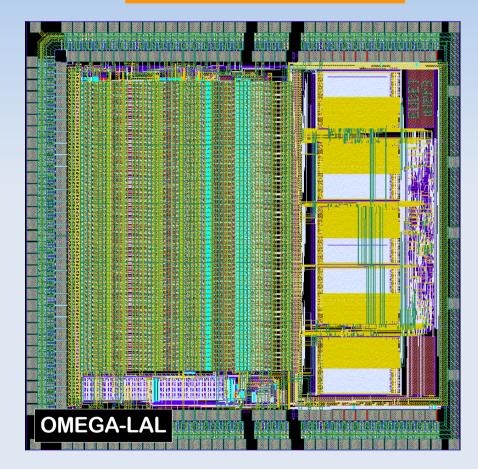

# HARDROC

- 64 channels, 16 mm<sup>2</sup>

- Digital/analogue output.

- 2 thresholds (3 very soon)

- Iow consumption

- ► < 10 µW/ch

- Power pulsing

- Digital memory

- 128 events

- ► ASIC ID, BC ID, hits

- Large gain range

- Channel wise

- X-talks < 2%</p>

- Threshold > 10 fC

- Adequate for GRPC\*

Prototype for 2<sup>nd</sup> gen. of ROC ASIC's (incl. local storage)

→ ECAL, AHCAL

### 2<sup>nd</sup> gen coming soon

\* For µMEGAS another ASIC is developed in IPNL with a threshold as low as 3 fC

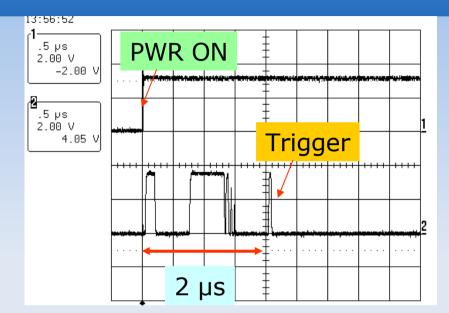

# **HARDROC:** Power pulsing

# **Going digital: Embedded electronics**

- 1 m<sup>2</sup>

- 10k channels

- 1 m<sup>3</sup> (40 layers)

- 400k channels

#### Embedded Readout chips

- ▶ 64 channels

- Daisy Chained

- Control & readout

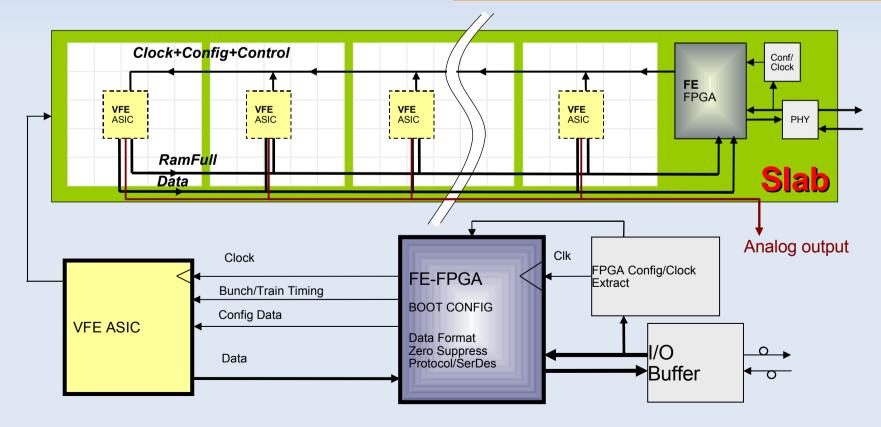

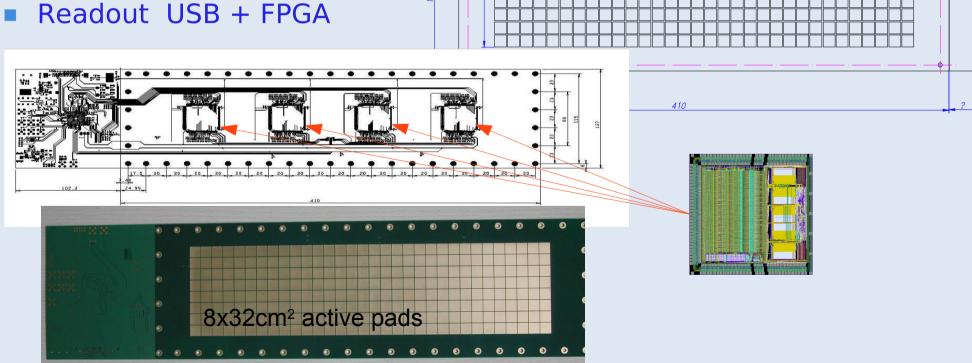

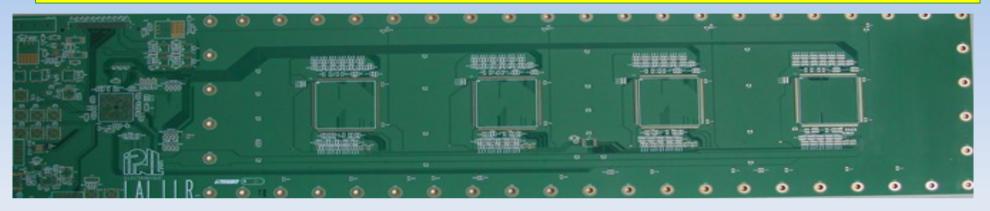

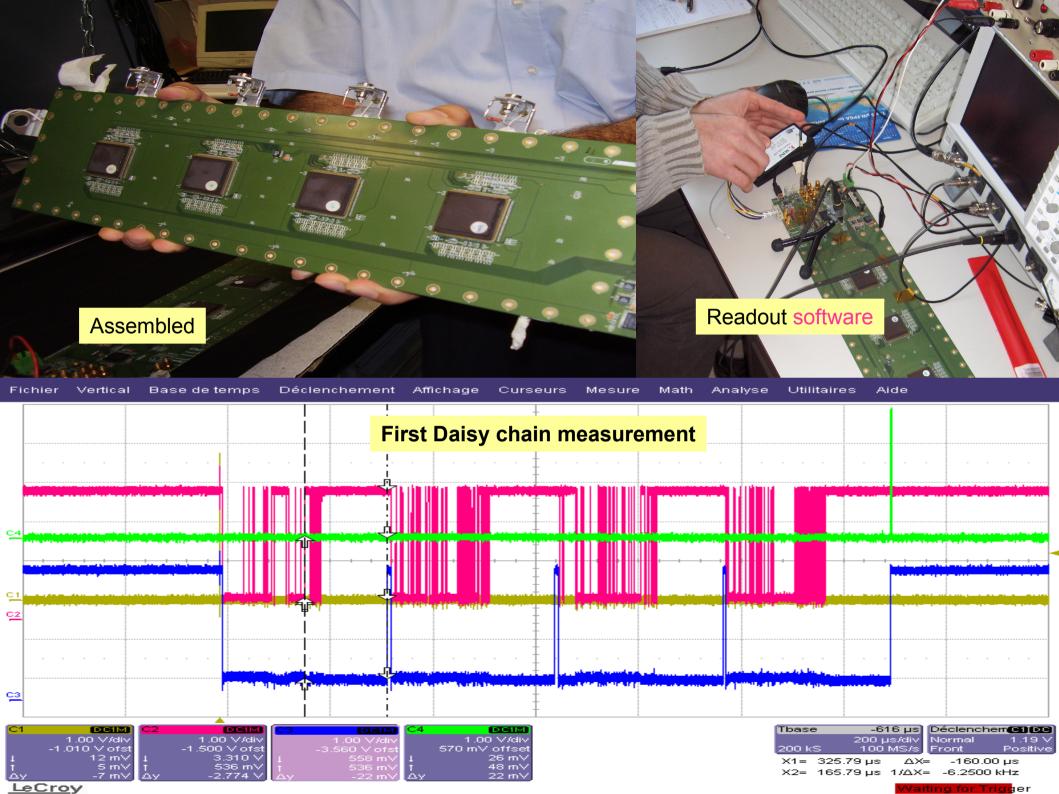

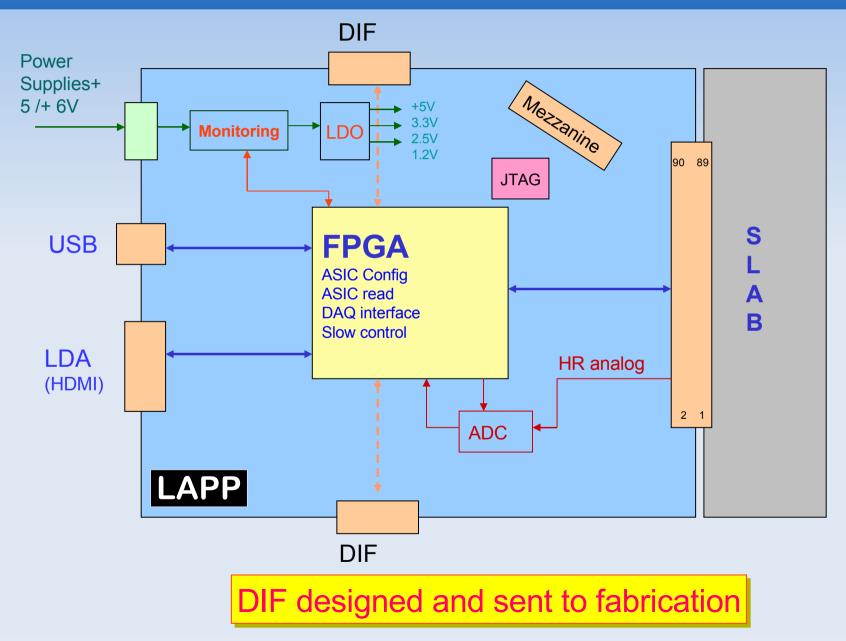

# **Readout system**

- The 4 chips are daisy-chained and connected to a FPGA communicating with a PC through a USB device.

- All components on the same PCB

- Firmware + Software (generic ROC interface library) developed

LLR

- Config loading

- Acquisition modes

- Readout & Debug

- Acquisition modes

- Internal triggers

- External triggers : cosmics & test beam

- Data output: The two kinds of data output of the HARDROC chips are accessible: digital and analogue

# **DHCAL1** test card

- $8 \times 32$  pads detector (GRPC and  $\mu$ MEGAS)

- 8-layer PCB

- 4 ASICs: HARDROC (Omega-LAL)

- ▶ 64 ch

- ► 2 thresholds

Vincent.Boudry@in2p3.fr Toward a m<sup>3</sup> DHCAL prototype – ECFA 2008, June 9-12, 2008, Warsaw

#### **June 07:**

- 8-layer PCB , 800 µm thick

- 8×32 pads of 1 cm<sup>2</sup> and 500 µm separation

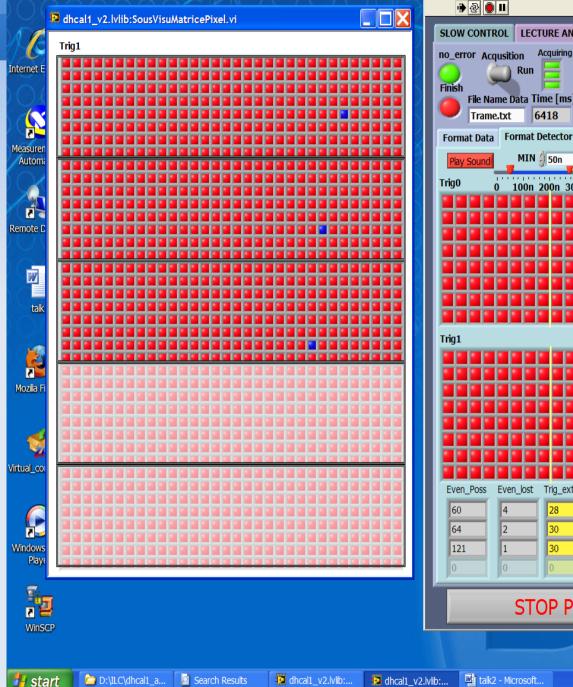

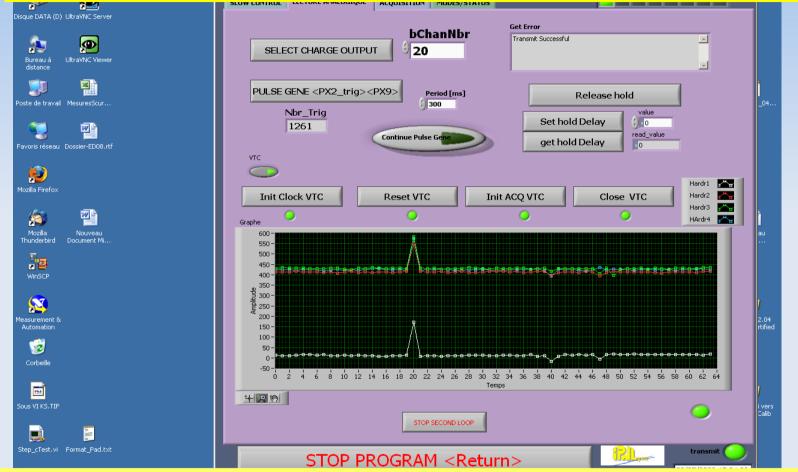

# Labview DAQ

Friendly labview based system was developed

\* Two thresholds

\* Gain value of each channel can be Chosen in [0-63]

Calibration is done automatically for all channels by injecting charge through internal capacitors

| LOW CONTROL LECTURE                                                                                                             |                | re ai     | ANALOGIQUE ACQU     |       |       | UISITION TESTS |             |                                        |                                                                                                                                              |      |           |              |

|---------------------------------------------------------------------------------------------------------------------------------|----------------|-----------|---------------------|-------|-------|----------------|-------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------|-----------|--------------|

|                                                                                                                                 |                | Get Error |                     |       |       | Device Info    |             |                                        |                                                                                                                                              |      |           |              |

| File_device<br>devices.tmp<br>File_registers<br>DHCAL1_Registers.csv<br>File_slowControlParameters<br>slowControlParameters.csv |                |           | Transmit Successful |       |       |                |             | ×                                      | Dev 0:<br>Flags=0x00000000<br>Type=0x00000000<br>ID=0x4C4C4448<br>SerialNumber=USB_DH1_00<br>Description=DHCAL1 BOARD<br>ftHandle=0x00000000 |      |           |              |

|                                                                                                                                 |                |           |                     |       |       | Read           | start setup | Rec                                    | all setup                                                                                                                                    | Sav  | e setup   | Delete setup |

| Slow Cont                                                                                                                       | trol Flag Sk   | ow Co     | ontrol              | cTest | Com   | ent Last Se    | etup        |                                        |                                                                                                                                              | _    |           |              |

|                                                                                                                                 |                |           |                     |       |       |                |             |                                        |                                                                                                                                              |      |           |              |

| Index                                                                                                                           | Name           | V         | alueASI             | C1    |       | ValueASIC2     |             | ValueAS                                | SIC3                                                                                                                                         |      | ValueASIC | 4            |

| 1                                                                                                                               | EN_RamFull     | 1         |                     |       |       | 1              |             | 1                                      |                                                                                                                                              | 1    |           |              |

| 2                                                                                                                               | EN_Dout        | 1         | 1                   |       |       | 1              |             | 1                                      |                                                                                                                                              | 1    |           |              |

| 3                                                                                                                               | En_Transmit(   | )n 1      |                     |       |       | 1              |             | 1                                      |                                                                                                                                              | 1    |           |              |

| 4                                                                                                                               | En_out_discri  | 1         |                     |       |       | 1              |             | 1                                      |                                                                                                                                              | 1    |           |              |

| 12-5                                                                                                                            | Header(7:0)    | 0         | DxAA                |       |       | 0x55           |             | 0xEE                                   |                                                                                                                                              | 0x77 |           |              |

| 13                                                                                                                              | bypass_chip    | 0         | 0                   |       |       | 0              |             | 0                                      |                                                                                                                                              | 0    |           |              |

| 14                                                                                                                              | EN_out_trig_i  | int 1     |                     |       | 1     |                | 1           |                                        | 1                                                                                                                                            |      |           |              |

| 15                                                                                                                              | EN_trig_int    | 1         |                     |       |       | 1              |             | 1                                      |                                                                                                                                              | 1    |           |              |

| 16                                                                                                                              | En_trig_ext    |           | 1                   |       |       | 1              |             | 1                                      |                                                                                                                                              |      | 1         |              |

| 17                                                                                                                              | EN_out_raz_i   | nt 1      | 1                   |       |       | 1              |             | 1                                      |                                                                                                                                              |      | 1         |              |

| 18                                                                                                                              | EN_raz_int     |           | 0                   |       |       | 0              |             | 0                                      | -                                                                                                                                            |      | 0         |              |

| 19                                                                                                                              | EN_raz_ext     |           | 1                   |       |       | 1              |             | 1                                      |                                                                                                                                              |      | 1         |              |

| 20                                                                                                                              | not_used       |           | 0                   |       |       | 0              |             | 0                                      |                                                                                                                                              |      | 0         |              |

| 84-21                                                                                                                           | Valid_trig(63: | 0) 0      | 0x00000000000000000 |       |       | 0x0000000      | 000000000   | 0x000000000000000000000000000000000000 |                                                                                                                                              |      |           |              |

| 94-85                                                                                                                           | dac0(9:0)      | -         | 0x200               |       | 0x200 |                | 0x200       |                                        | 0x200                                                                                                                                        |      |           |              |

| 104-95                                                                                                                          | dac1(9:0)      |           | 0x200               |       | 0x200 |                | 0x200       |                                        | 0x200                                                                                                                                        |      |           |              |

| 105                                                                                                                             | ON_otadac      | 1         |                     |       |       | 1              |             | 1                                      |                                                                                                                                              |      | 1         | T            |

| Name  One Asic  Old_Value  Replace One Asic  New_Value    preamp_gain(0)(5:0)  ValueASIC2  10  Replace All Asic  10             |                |           |                     |       |       |                |             |                                        |                                                                                                                                              |      |           |              |

| Replace One Asic All Gain<br>Replace All Asic All Gain<br>modif?                                                                |                |           |                     |       |       |                |             |                                        |                                                                                                                                              |      |           |              |

| CLOSE USB INIT USB Send Slow Control                                                                                            |                |           |                     |       |       |                |             |                                        |                                                                                                                                              |      |           |              |

| STOP PROGRAM <return></return>                                                                                                  |                |           |                     |       |       |                |             |                                        |                                                                                                                                              |      |           |              |

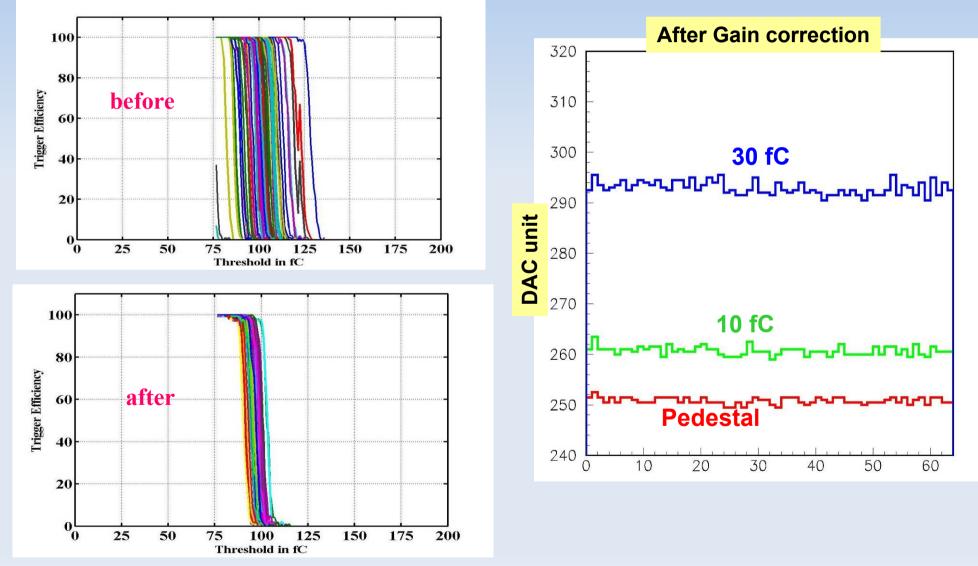

### **HArDROC : S-curves of 64 channels**

#### Using on chip electronic calibration

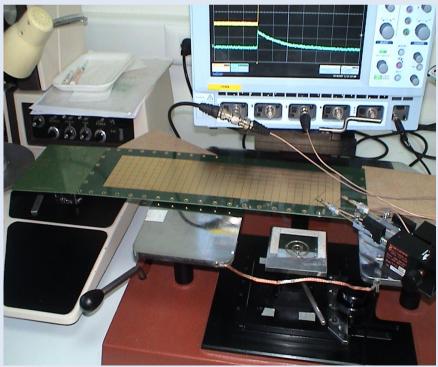

# **Cosmic bench**

My Computer

####

2 🔿 🕹 🔵 🗉 SLOW CONTROL LECTURE ANALOGIQUE ACQUISITION MODES/STATUS PCB Acquiring Acq\_Stop Period multi Trig\_Int 26 Get Error cut to Data л Transmit Successful 300 [ms] 43 Raz 118 File Name Data Time [ms] Nbr Trig befor Read Trig ext 234 START ACCOUISITION STOP and READ DATA 30 init\_file Pulse\_gépé **RESET ALL** Format Data Format Detector Image Detector Calibration Visu Monitor Status ortcut to **Time Window** 275n MAX Range Max in Calib Time Window 1u 1m 1s 10s 100n 200n 300n 400n 500n 600n 700n 800n 900n 1u RESET Nbr\_TRIG0 Display/Clear Display\_All\_Detector Pad Coord Nbr\_TRIG1 SB FUG Trig\_ext\_lost Compteur[s] Num\_Even Efficacité[%] Trig\_ext\_lost[%] Even\_Poss Even\_lost Trig\_ext 96.43 53.57 15 100n 43.33 96.67 13 100n 29 DISPLAY 28 93.33 43.33 13 100n 0.00 0.00 transmit STOP PROGRAM <Return> 23/04/2008 12:04:59 **R.DELLA NEGRA** rtcut to Format Calib

Vincent.Boudry@in2p3.fr Toward a m<sup>3</sup> DHCAL prototype – ECFA 2008, June 9-12, 2008, Warsaw

FR 🔇 📻 📓 📃 12:05

### **First results**

| TFE       | 93%             |

|-----------|-----------------|

| Isobutene | <mark>5%</mark> |

| SF6       | 2%              |

#### Threshold $\approx 100 \text{ fc}$

# Analog readout was recently integrated and will be used to chose the thresholds adequately

Amplitude of the signal injected in one of the 64 channels of each of the 4 ASICs through internal capacitors

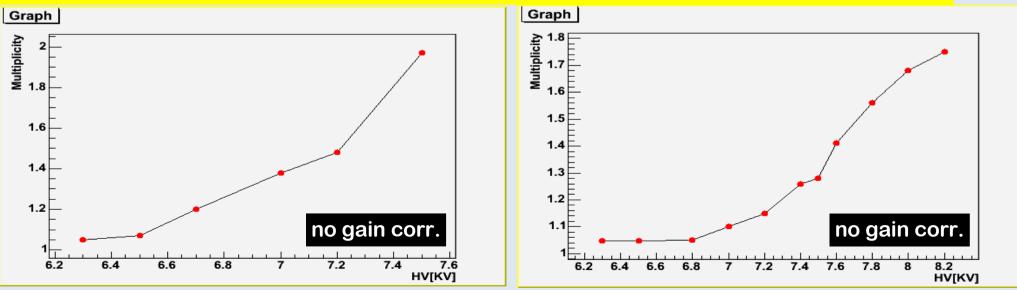

### **Beam tests**

- 5 fully equipped detectors (32×8 pads each):

GRPC & µMEGAS

- 10-17 July : CERN PS

- $\mu$ , low energy  $\pi$ 's

- 3-11 August : CERN SPS

- higher energy  $\mu$ ,  $\pi$ , e's

- Program:

- Efficiency and multiplicity

- vs: angle, position, particle multiplicity

- but also the first phase of the Hadronic shower

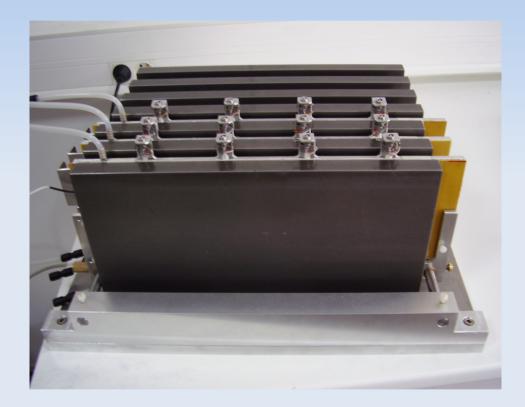

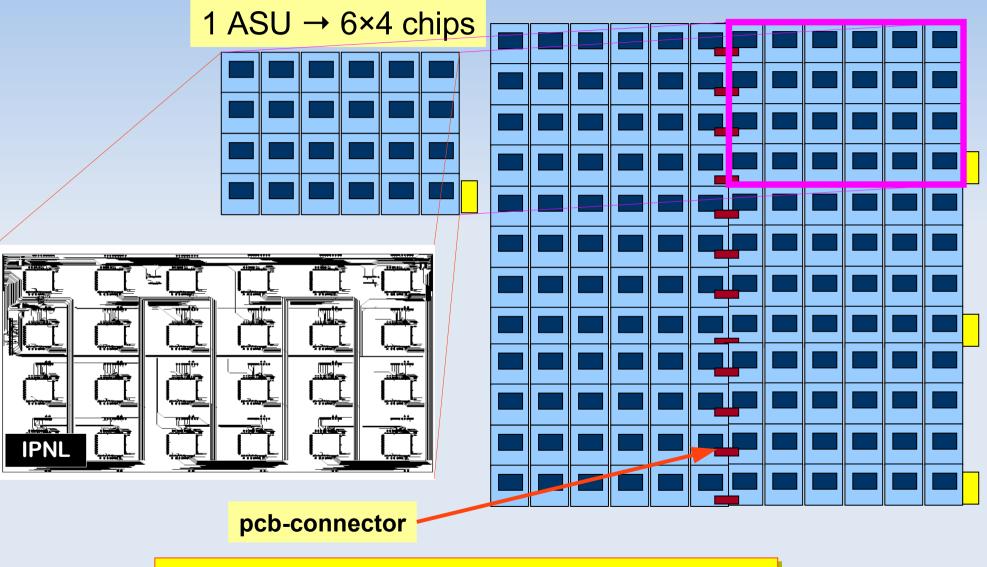

# Next steps: m<sup>2</sup> ASIC support Units

ASU hosting 24 HARDROC chips designed

Vincent.Boudry@in2p3.fr Toward a m<sup>3</sup> DHCAL prototype – ECFA 2008, June 9-12, 2008, Warsaw

# Connection between the different ASU is under study: signal transmission+ mechanics (IPNL+CIEMAT)

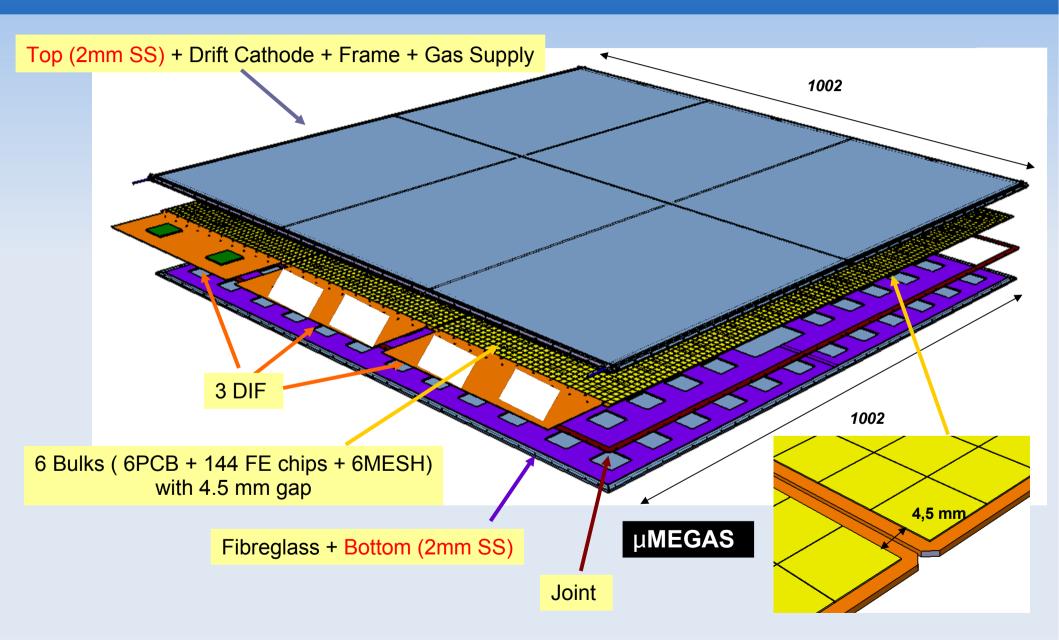

# Mechanical design of a 1 m<sup>2</sup> prototype

# **Detector InterFace card**

Vincent.Boudry@in2p3.fr Toward a m<sup>3</sup> DHCAL prototype – ECFA 2008, June 9-12, 2008, Warsaw

# **First test of EUDET DAQ2**

# Next step: m<sup>3</sup>

### Perspectives A 1 m<sup>3</sup> technological prototype ILC-Module0 to be built before 2010

The technological prototype design optimization on going

# **Conclusions & perpectives**

- A Digital HAdronic CALorimeter with semi-digital (2-3 thr.) readout is very promising candidate for future collider experiments

- ▶ integration work going on  $\Rightarrow$  see ILD & SiD pres.

- Small & big GRPC & µMEGAS detectors realised and tested

- A multi-slice test based on the **embedded** semi-digital readout was successfully tested in a laboratory cosmic bench

- A beam test is scheduled next month at CERN.

- 1 m<sup>2</sup> project is ongoing and the first plane is expected before the end of 2008.

- A full 1 m<sup>3</sup> technological prototype is funded and expected in 2009-2010

Energy Resolution

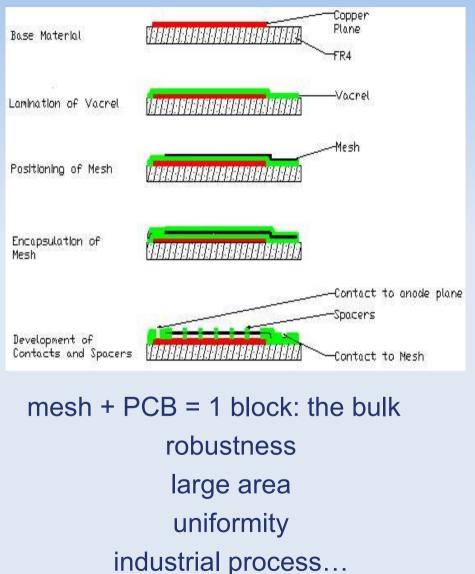

# Micro Mesh gaseous structure

# **MicroMegas Prototypes**

# PCB and bulk from CERN (Rui de Oliveira)

- 325 LPI mesh

- spacers : 120 µm height 300 µm diameter

- ▶ pads : 0.98×0.98 cm<sup>2</sup>, 200 µm between pads

### The chamber

- 95% Argon, 5% Isobutane

- conversion volume (3mm)

- a top in Stainless Steel with a copper drift cathode

### The pad readout : analogue

- Gassiplex board : 6 gassiplex chips 96 channels Electronics card built for CAST by DAPNIA (P. Colas, Philippe Abbon)

- VME sequencer and ADC from CAEN

- CENTAURE acquisition (SUBATECH, Nantes, D.Roy)

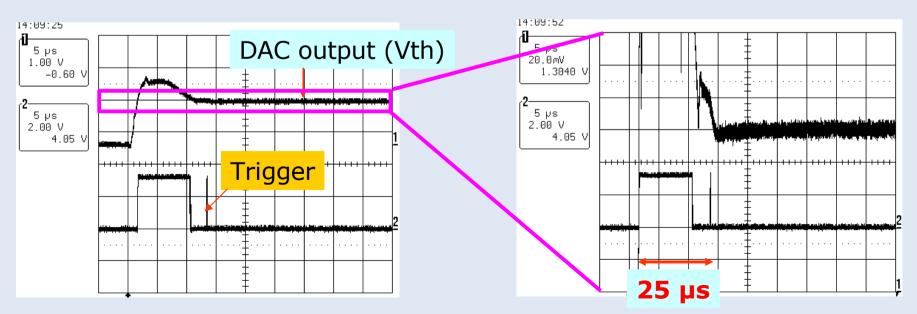

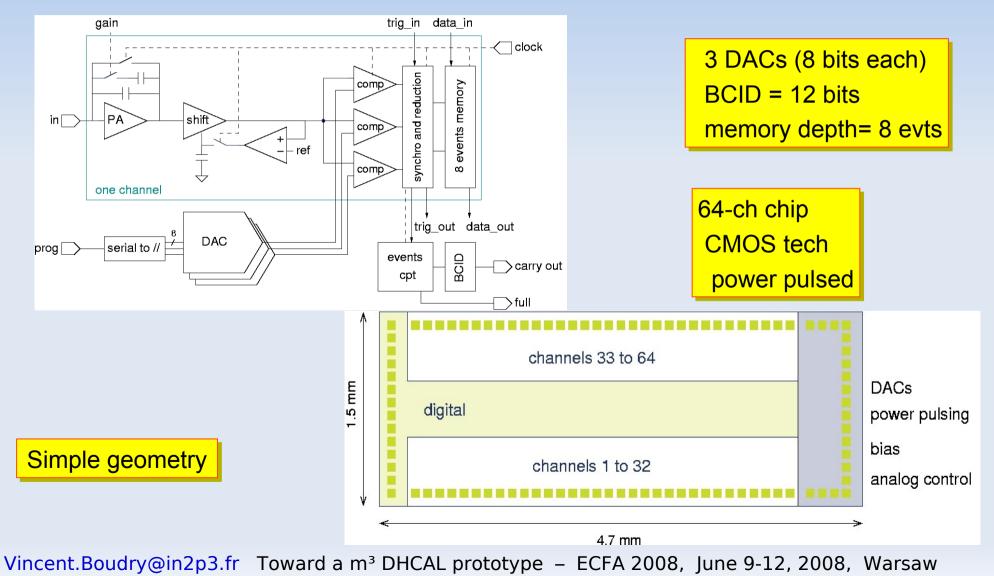

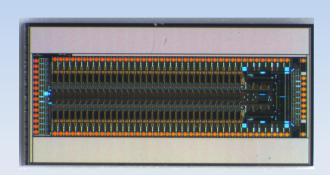

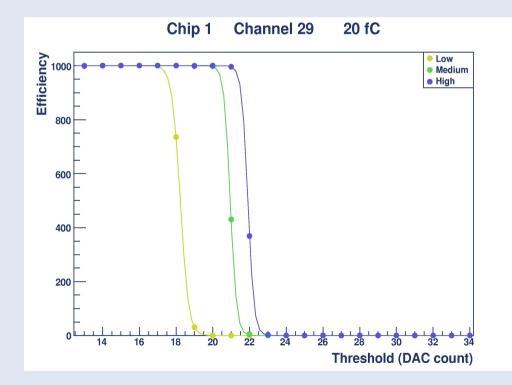

# **DIRAC ASIC**

# A new chip with a low threshold for µMEGAS is under development @IPNL

The chip was designed and produced. A test board using OPERA DAQ developed @IPNL was used.

First results: Mode µMEGAS 0.8 fc/DAQ Resolution < 2.5 fc

Tests and improvement are going on